Digital-electronics 简明教程

Clock Signal and Triggering

在本章中,让我们逐个讨论时钟信号及其触发类型。

In this chapter, let us discuss about the clock signal and types of triggering one by one.

Clock Signal

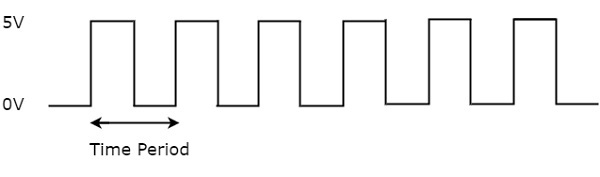

时钟信号是一个周期性信号,其导通时间和截止时间不必相同。当其导通时间和截止时间相同时,我们可以表示时钟信号为 square wave 。该时钟信号如下图所示。

Clock signal is a periodic signal and its ON time and OFF time need not be the same. We can represent the clock signal as a square wave, when both its ON time and OFF time are same. This clock signal is shown in the following figure.

在上图中,方波被视为时钟信号。该信号在逻辑高电平 (5V) 保持一段时间,并在逻辑低电平 (0V) 保持相同的时间量。此模式以一定时间周期重复。在这种情况下, time period 将等于导通时间的两倍或截止时间的两倍。

In the above figure, square wave is considered as clock signal. This signal stays at logic High (5V) for some time and stays at logic Low (0V) for equal amount of time. This pattern repeats with some time period. In this case, the time period will be equal to either twice of ON time or twice of OFF time.

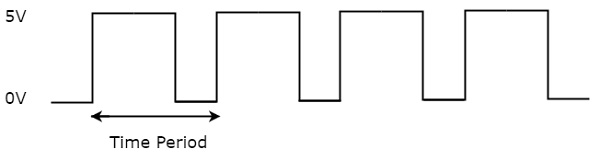

当导通时间和截止时间不相同时,我们可以将时钟信号表示为 train of pulses 。该时钟信号如下图所示。

We can represent the clock signal as train of pulses, when ON time and OFF time are not same. This clock signal is shown in the following figure.

在上图中,脉冲序列被视为时钟信号。该信号在逻辑高电平 (5V) 保持一段时间,并在逻辑低电平 (0V) 保持另一段时间的。此模式以一定时间周期重复。在这种情况下, time period 将等于导通时间和截止时间的和。

In the above figure, train of pulses is considered as clock signal. This signal stays at logic High (5V) for some time and stays at logic Low (0V) for some other time. This pattern repeats with some time period. In this case, the time period will be equal to sum of ON time and OFF time.

时钟信号时间周期的倒数称为时钟信号的 frequency 。所有顺序电路都使用时钟信号进行操作。因此,必须根据时钟信号频率选择顺序电路可以相应操作的频率。

The reciprocal of the time period of clock signal is known as the frequency of the clock signal. All sequential circuits are operated with clock signal. So, the frequency at which the sequential circuits can be operated accordingly the clock signal frequency has to be chosen.

Types of Triggering

以下是用于顺序电路的两种可能的触发类型。

Following are the two possible types of triggering that are used in sequential circuits.

-

Level Triggering

-

Edge Triggering

Level Triggering

时钟信号中存在逻辑高电平和逻辑低电平两个电平。以下是两种 types of level triggering 。

There are two levels, namely logic High and logic Low in clock signal. Following are the two types of level triggering.

-

Positive Level Triggering

-

Negative Level Triggering

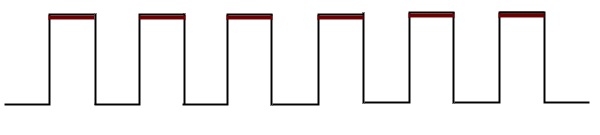

如果在时钟信号处于 Logic High 时用时钟信号操作顺序电路,那么这种触发类型称为 Positive level triggering 。它在下面的图中突出显示。

If the sequential circuit is operated with the clock signal when it is in Logic High, then that type of triggering is known as Positive level triggering. It is highlighted in below figure.

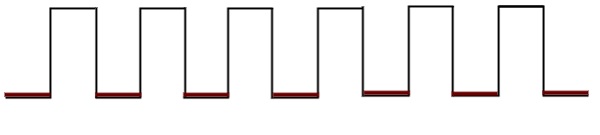

如果在时钟信号处于 Logic Low 时用时钟信号操作顺序电路,那么这种触发类型称为 Negative level triggering 。它在下面的图中突出显示。

If the sequential circuit is operated with the clock signal when it is in Logic Low, then that type of triggering is known as Negative level triggering. It is highlighted in the following figure.

Edge Triggering

时钟信号中会发生两种类型的转换。这意味着时钟信号要么从逻辑低电平转换为逻辑高电平,要么从逻辑高电平转换为逻辑低电平。

There are two types of transitions that occur in clock signal. That means, the clock signal transitions either from Logic Low to Logic High or Logic High to Logic Low.

以下内容将基于时钟信号的转换来说明 types of edge triggering 。

Following are the two types of edge triggering based on the transitions of clock signal.

-

Positive Edge Triggering

-

Negative Edge Triggering

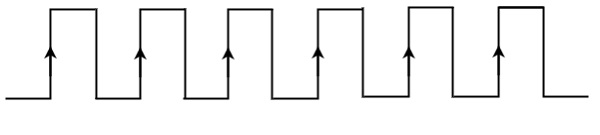

如果顺序电路中运用了时钟信号使其从逻辑低电平向逻辑高电平转换,则该触发类型被称为 Positive Edge Triggering 。它也可以称为上升沿触发。它如下图所示。

If the sequential circuit is operated with the clock signal that is transitioning from Logic Low to Logic High, then that type of triggering is known as Positive Edge Triggering. It is also called as rising edge triggering. It is shown in the following figure.

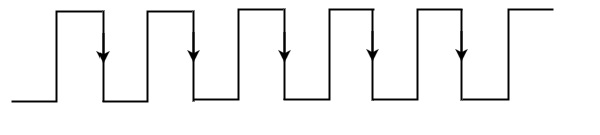

如果顺序电路中运用了时钟信号使其从逻辑高电平向逻辑低电平转换,则该触发类型被称为 Negative Edge Triggering 。它也可以称为下降沿触发。它如下图所示。

If the sequential circuit is operated with the clock signal that is transitioning from Logic High to Logic Low, then that type of triggering is known as Negative Edge Triggering. It is also called as falling edge triggering. It is shown in the following figure.

在接下来的章节里,我们将讨论基于触发类型的不同顺序电路。

In the coming chapters, we will discuss about various sequential circuits based on the type of triggering that can be used in it.